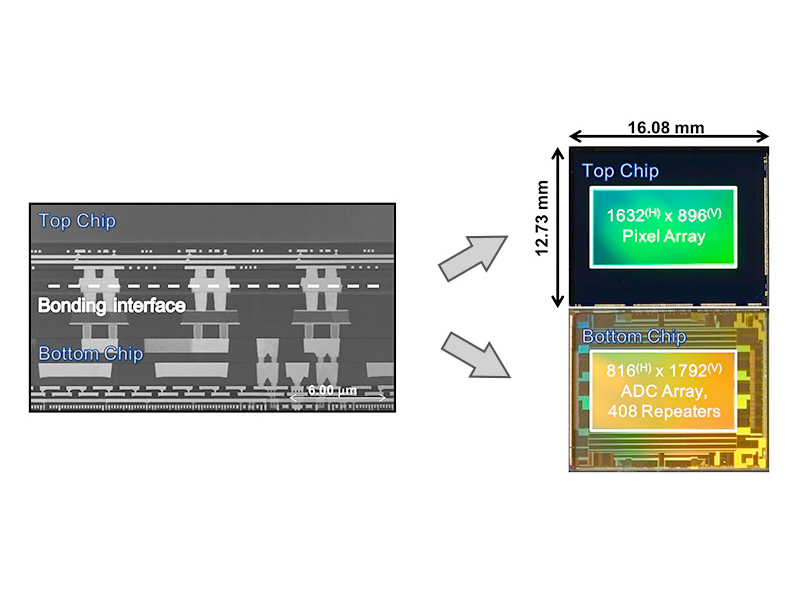

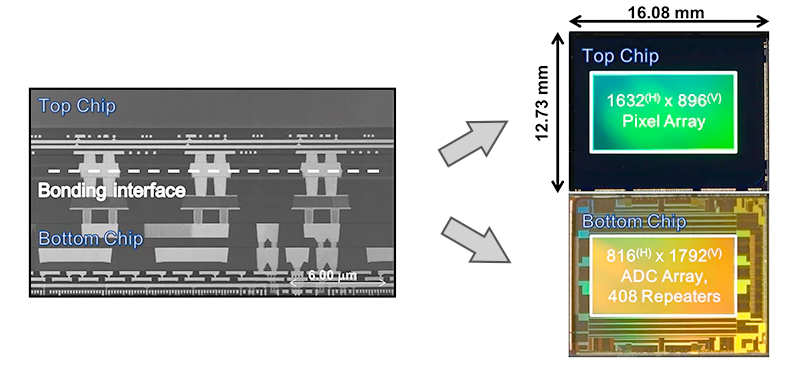

▲(左)接合部断面構造 (右上)画素基板 (右下)ロジック基板

ソニーは、グローバルシャッター機能(※1)を実現する画素並列A/D変換器搭載 裏面照射型CMOSイメージセンサーを開発した。2018年2月11日(日)から米・サンフランシスコで開催の ISSCC(国際固体素子回路会議)において発表された。

※1 画素信号を1行毎に読み出す為に起こるCMOSイメージセンサー特有の画像の歪み(フォーカルプレーン歪み)を解消する機能。

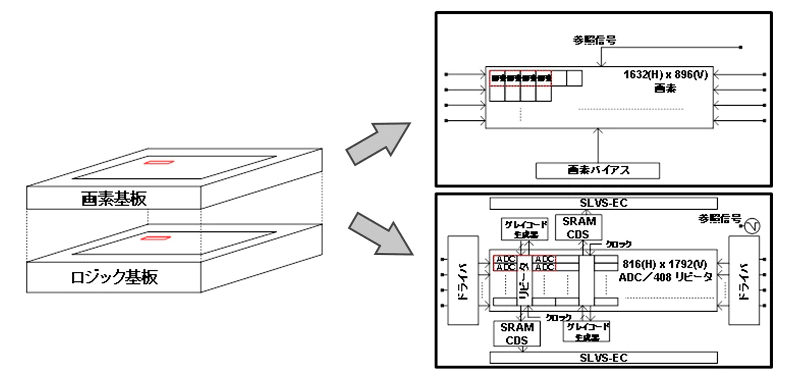

▲概略ブロック図

おもな特徴

高感度な裏面照射型CMOSイメージセンサーでグローバルシャッター機能をおもに以下の技術で実現。

●低電流動作可能で小型の画素並列A/D変換器

低消費電力化の為に、サブスレッショルド領域で動作する、業界最高性能(※3)の低電流動作可能で小型の14ビットA/D変換器を開発。従来のカラムA/D変換方式(※2)に比べて、およそ1,000倍もの数のA/D変換器の搭載により増大する電流の課題を克服。

●Cu-Cu(カッパー・カッパー)接続

全画素並列のA/D変換を実現する為、約300万個もの「Cu-Cu(カッパー・カッパー)接続(※4)」を可能とする技術を開発。本技術により、画素基板とロジック基板を導通させ、有効画素数と同じ146万個ものA/D変換器、およびデジタルメモリーの搭載スペースを確保。

●高速データ転送機構

146万個ものA/D変換器の動作に伴う、大量のデジタル信号転送を可能にするリピータ回路を新たに開発。これにより、全画素のデジタル信号を高速に読み書き可能。

※2 A/D変換器を画素の垂直列毎に並列配置した方式。

※3 FoM(Figure of Merit):0.24e-・nJ/step。(消費電力×ノイズ)/(画素数×フレーム速度×ADC分解能)。

※4 裏面照射型CMOSイメージセンサー部(上チップ)とロジック回路部(下チップ)を積層する際に、Cu(銅)のパッド同士を接続することで電気的導通を図る技術。画素領域の外周の貫通電極により、上下のチップを接続するTSV(シリコン貫通電極)に比べて、設計自由度や生産性の向上、小型化、高性能化などが可能。

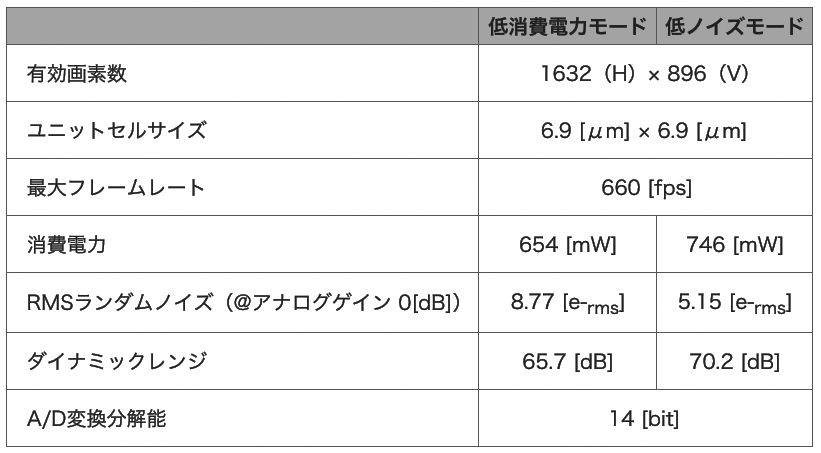

おもな仕様

ソニー株式会社

https://www.sony.co.jp/